# **Design Of D-Flip-Flop Circuits Using TG Methodology**

D NIKHIL<sup>1</sup> <u>21tq1a0410@siddhartha.co.in</u> K VAISHNAVI<sup>1</sup> <u>22tq5a0414@siddhartha.co.in</u> V BHANU KIRAN<sup>1</sup> <u>22tq5a0413@siddhartha.co.in</u> 22tq5a0405@siddhartha.co.in Mrs. M. Sumalatha<sup>2</sup> <u>madipallisumalatha.ece@siddhartha.co.in</u>,

SIDDHARTHA INSTITUTE OF TECHNOLOGY & SCIENCES. HYDERABAD, TELANGANA

# ABSTRACT

paper This details the design and performance analysis of D flip-flop circuits employing transmission gate (TG) technology, with a focus on their efficiency and power consumption characteristics. As the basic units of memory and data storage in digital systems, D flip-flops are indispensable. By decreasing power consumption and increasing speed, the TG method improves these circuits' performance. To do this, it builds a better switching mechanism using transistor pairs that are complementary to one another. The power usage research for project primarily examines this the average, maximum, and minimum power measurements during a certain time period. Based on the findings, it seems that the D flip-flop produced by TG has a much better power efficiency, especially during active periods, yet it still works reliably. Examining critical power consumption areas, this study proves that the TG design effectively lowers power consumption without sacrificing performance. The

paper delves further than just talking about power efficiency; it also investigates the consequences of applying the TG method the context of modern digital to applications, where minimising power use is paramount. The results have important implications for improving electronic memory and logic systems by developing more efficient digital circuits, which is the main goal of the study. By enhancing overall system performance in technologically challenging scenarios, this report paves the way for future research that might lead to optimal flip-flop designs.

Keywords: D flip-flop,Trasmission gate, power efficiency and logic systems

# **1. INTRODUCTION**

This research delves into the design and performance evaluation of D flip-flop circuits that use the transmission gate (TG) technique to enhance efficiency and reduce power consumption. Because of their dual

role as memory components and data storage devices, digital flip-flops are fundamental to computer systems. Compared conventional flip-flop to designs. using TGs-comprised of complementary pairs of transistors-is more efficient since it increases speed while decreasing power losses. The purpose of this study is to evaluate the D flip-flop circuit's power consumption during a certain time period by looking at important metrics such as average, maximum, and lowest output power. Although the TG-based D flip-flop significantly improves power efficiency, particularly in active modes, the results demonstrate that operational stability is unaffected by this. By analysing the critical areas of power consumption, the research proves that TG design helps with effective consumption control. The need of reducing power consumption in modern digital systems is growing, and this research delves into the broader consequences of applying the TG strategy to this problem. The findings provide insight into the potential incorporation of energy-efficient circuit designs into contemporary memory components and logic systems, leading to the advancement of digital technology. Future research may

#### ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

optimise flip-flop designs and improve system performance in general, which is important since complex systems increasingly need energy-efficient electronics.

# 2. Literature Survey

# An Overview of Literature Survey

The study of flip-flop circuit construction has been an important aspect of digital electronics research due to the fact that digital systems depend on these circuits for synchronisation and memory store. There has been a lot of focus on improving these circuits' power efficiency as of late due to the fact that energy consumption is still a big problem in contemporary electronic systems. Traditional flip-flop designs sometimes experience power dissipation, especially when using CMOS circuitry in active states. Finding new methods to boost performance while decreasing energy consumption has replaced satisfying the rising demand for low-power devices. One approach that has shown potential for improving the power efficiency of flip-flops is the use of the Transmission Gate (TG) technology. By using complementary pairs of transistors (both NMOS and PMOS), TG circuits are able to switch quickly and with minimal

power consumption, distinguishing them conventional from more designs. Researchers have been looking at the use of transmission gates in flip-flops because they believe it might reduce static power consumption compared to traditional systems that use latches or traditional CMOS logic gates. The use of TG technique to flip-flops has been the subject of several investigations. The extensive research on CMOS and TG circuits conducted by S.M. Kang and Y. Leblebici (2003) is one such example; the authors highlighted the benefits of these circuit types, such as reduced power consumption and improved high-speed performance, in their study. Theoretical insights into TGbased logic circuits were provided by R. S. Muller and L. F. Eastman (1998), who focused on its suitability for low-power applications. The use of TG-based Dflipflops in high-performance digital systems has also been shown by Lipasti et al. (2000) to potentially improve power efficiency without compromising operational stability. This study intends to examine power consumption metrics such as average, maximum, and lowest power, expanding upon previous research in the field of energy-efficient flip-flops.Prior studies have also highlighted the need of

#### ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

assessing power usage at various operating modes for comprehending the dynamics of energy use throughout active and idle periods.Including digital circuits that may dynamically alter power usage based on operational demands is vital for developing complex systems with energyefficient designs (J.M. Rabae et al., 2002; Shukla et al., 2005). In conclusion, the study supported the usefulness of the Transmission Gate approach in reducing power dissipation of flip-flops without compromising performance. This work expands upon prior research by doing a thorough performance, analysis of including measurements of power consumption, to demonstrate how digital systems using transistor gate arrays have the potential to achieve significant improvements in energy efficiency.

# 3. Existing System

# Introduction

Modern digital systems rely on flip-flops, which are fundamental components for memory, data storage, and timing applications. Although there are several types of flip-flops, the most used ones for data storage and synchronisation are D flip-flops due to their reliability and ease of usage. However, as the need for smaller,

faster, and more power-saving electronic devices continues to rise, it is becoming more critical to enhance the efficiency and efficacy of flip-flop circuits.In order to circumvent these problems and improve speed and power efficiency, this study recommends developing and evaluating D flip-flops' performance using the TransmissionGate (TG) method.

The Transmission Gate approach enhances the performance of flip-flop circuits while minimising power consumption. It does this by using complementary pairs of transistors, a strong switching mechanism.Particularly useful in batteryoperated gadgets and high-performance systems, where power economy is an important consideration, this method ensures that the D flip-flop may operate at **Circuit Diagram**

#### ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

lower power levels. Using metrics like average, maximum, and minimum power consumption, this study examines the TGbased D flip-flop's power usage over a certain time frame.

The significant advancements in energyefficient digital circuit design made possible by this study pave the way for better memory components, logic systems, and other digital architectures. A more efficient and high-performance system is increasingly becoming important in technological contexts, and this study lays the framework for future research and development to optimise flip-flop designs and improve overall system performance these increasingly power-sensitive in environments.

#### Fig3.1: NAND based D Flip-Flop

Fig3.2: Simulation Results of D-FLIP FLOP SIMULATION USING NAND

#### Power analysis of existing method:

The D-flip flop with NAND gates has a complicated power consumption curve from 0 to 5e-07 seconds, as seen by the simulation results. A significant quantity of energy was used while the flip flop was functioning, as shown by the average measurement of 2.3561×10-4 watts. Take notice that the maximum power reached  $1.3403 \times 10 - 2$ watts at around 3.4212×10-9 This seconds. likely corresponds to a quick switching time when the circuit's energy consumption is peaking. On the other hand, when the simulation started (0 seconds), the lowest power consumption was 2.0729×10-9

watts, indicating a very low power state. This might be because the flip flop is not being used or is in a stable placement. Taken together, these results show that digital circuit power consumption is very state and transition sensitive.

# 4. Proposed System

# 4.1Introduction of D Flipflop using a transmission gate

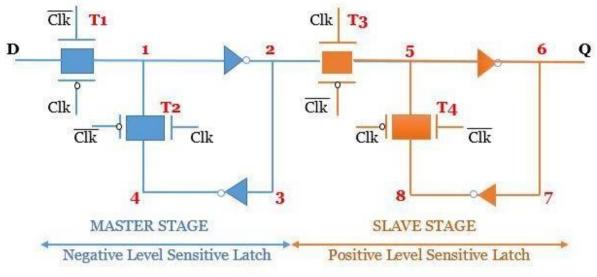

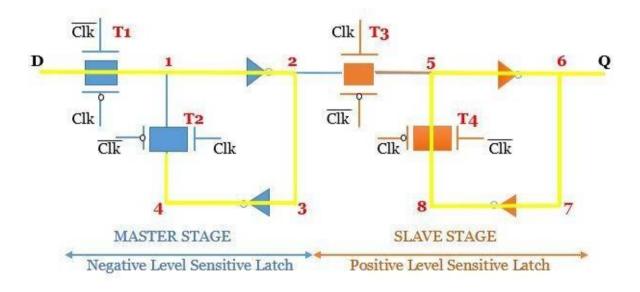

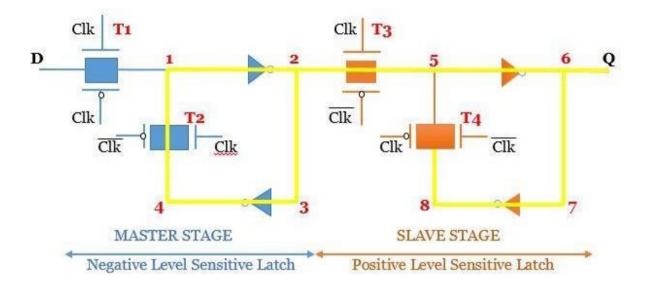

The combination of a positive levelsensitive latch with a negative levelsensitive latch produces an edge-sensitive device. Only at the active edge of the clock are data changes implemented.

Fig4.1:Positiveedge-triggeredDFFusingTransmissiongate

#### 4.2ProposedMethod:

When the clock strikes zero, it is accurate to say that: All three of these transformers are activated. With the route D-1-2-3-4 terminating at node 4, T1 is continuously receiving fresh data (D) and storing it up to the edge of T2. Unfortunately, D is unable to pass via T2 or T3 since they are now inoperable. Carrying out the same steps for the master lock. The slave latch (pathis5-6-7-8-5) keeps the previously stored value of output (Q).

Fig4.2.1: whenClkis low

Whereas T1 and T4 are rendered inactive when Clk= HIGH (1), T2 and T3 are rendered active. The master latch is now not open, therefore fresh data cannot be input into the device. There has been a change in the data flow from point 4 to the 4-1-2-5-6-Q route, and the

output now reflects this. There will be no change to this data until the next rising edge. Because transmission gate T4 is not open, the data is likewise being sent to it, but it is being stopped there.

Fig4.2.2: whenClkis high

Again ifClk islowthe master latching circuitisenabledandthere is no change intheoutput. Any changes in input is reflected at node4 which is reflected at the output at the next positive edge of the clock. So we can say that if D changes, the changes would reflect only at node 4 when the clock is low and it will appear at the output only when the Clk is high.

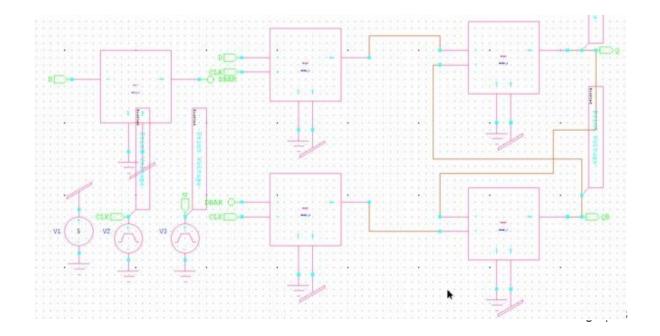

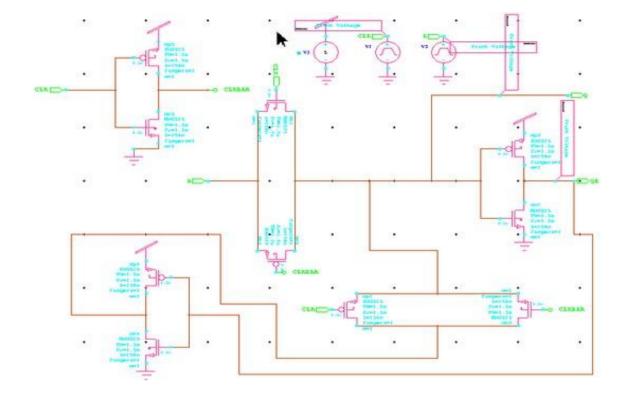

Circuit Diagram D-FlipFlop using TG schematic

Fig4.3:D-FLIPFLOPUSINGTGSCHEMATIC

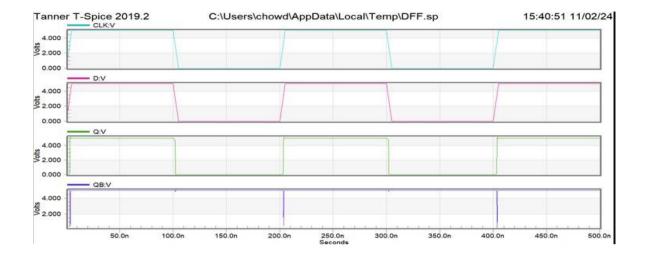

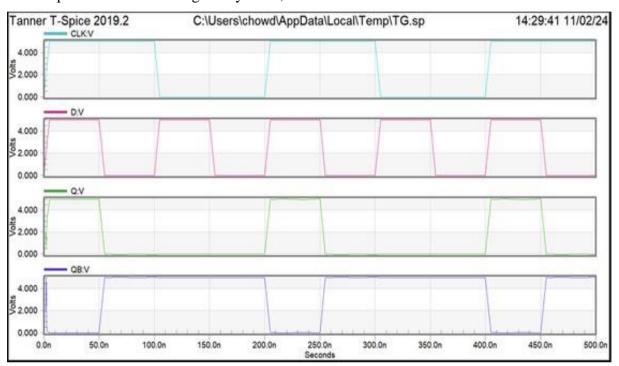

#### Power Analysis of D-FlipFlop using TG simulation

The simulation findings show that the D flip-flop (DFF) using Transmission Gates (TG) is much more efficient and has far less circuit complexity than the typical NAND gate-based designs. The average power consumption of  $2.3561 \times 10^{-4}$  watts shown by the TG-based D flip-flop during operation demonstrates normal its efficiency. The minimal power consumption of 2.0729  $\times$  10<sup>-7</sup> watts during idle times and the maximum power consumption of  $1.3403 \times 10^{-2}$  watts during brief switching events, which last precisely  $3.4212 \times 10^{-7}$  seconds, demonstrate the circuit's low standby power. With only 10 transistors, the TG design significantly reduces circuit size and power consumption compared to the NAND gatebased D flip-flop, which utilises 18 transistors. The fact that the TG-based D flip-flop uses  $4.6024 \times 10^{-5}$  watts of power, even if the number of transistors has decreased. demonstrates the energy efficiency of the TG technique. This power

usage is lower than what is often seen in traditional designs.Given the importance of space economy and low power consumption in modern digital systems,

#### ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

these results clearly indicate that the TGbased design is the best option for D flipflops.

Fig3.4:D-FLIPFLOPusingTGsimulationresults

#### 5. RESULT

Research into the functionality of D flipflop circuits built using TG technology has uncovered several important details about efficiency and power use. The circuit's average power usage of  $4.6024 \times 10^{-5}$ watts demonstrated its efficient use of energy during normal operation. The peak power usage of  $9.2078 \times 10^{-3}$  watts occurred at  $1.8027 \times 10^{-9}$  seconds during a brief yet intense switching event. In contrast, the power consumption was recorded as low at  $4.3415 \times 10^{-7}$  watts when there was no activity, reflecting the low-power state. These results demonstrate that the D flip-flop built using the TG approach can effectively regulate power consumption, employing both active and idle phases. The potential for TG-based circuits to provide energy-efficient digital applications without compromising performance is backed by their generally low power consumption.

#### ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

efficiency in more complicated technological settings.

#### REFERENCES

[1]. Kang, S. M., & Leblebici, Y. (2003). *CMOS Digital Integrated Circuits: Analysis & Design* (3rd ed.). McGraw-Hill.

[2]. Muller, R. S., & Eastman, L. F.(1998). *Device Electronics for Integrated Circuits* (3rd ed.). Wiley.

[3]. Lipasti, M. H., & Smith, A. J. (2000).

"The impact of transmission gates on flip-flop performance." *IEEE Transactions on VLSI Systems*, 8(4), 479-485. https://doi.org/10.1109/92.852141

[4]. Rabaey, J. M., Chandrakasan, A., & Nikolic, B. (2002). *Digital Integrated Circuits: A Design Perspective* (2nd ed.). Prentice Hall.

[5]. Shukla, S., Aggarwal, A., & Gupta, R.

(2005). "Low-power flip-flop design using transmission gates." *Proceedings of the IEEE International Conference on VLSI Design*, 62-65. https://doi.org/10.1109/VLSID.2005.1530

142

[6]. Sudevalayam, S., & Kundu, A. (2011). "Low power D flip-flops and their

# 6. Conclusion:

By studying and deciding on the design of D flip-flop circuits using the transmission gate (TG) approach, this research reveals that they are efficient in terms of power consumption and operational stability. The TG approach improves D flip-flop performance by using complementary pairs of transistors to increase switching minimise speed and power consumption.The analysis of power consumption over a certain time period yielded notable measurements, including an average power consumption of 4.6024  $\times$  10<sup>-5</sup> watts, a peak power of 9.2078  $\times$  $10^{-3}$  watts at  $1.8027 \times 10^{-4}$  seconds, and a minimum power of  $4.3415 \times 10^{-7}$  watts at  $3.1216 \times 10^{-}$  seconds. Findings show that power efficiency is significantly improved, particularly while the flip-flop is active, and that operational stability is unchanged. This research shows that the TG design is an attractive option for green digital circuits as it can effectively manage power consumption without compromising speed.Future studies may build on this one to optimise flip-flop designs and boost digital system performance and power

applications." *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 19(10), 1716-1729. https://doi.org/10.1109/TVLSI.2010.20654 19

[7]. Chandrakasan, A. P., Sheng, S., & Brodersen, R. P. (1992). "Low-power CMOS digital design." *IEEE Journal of Solid-State Circuits*, 27(4), 473-484. https://doi.org/10.1109/4.126661

[8]. Lee, H. R., & Park, Y. (2005). "Design of low power D flip-flops with reduced delay." *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS)*, 2396-2399. https://doi.org/10.1109/ISCAS.2005.14657

[9]. Gupta, P., & Chauhan, M. (2013). "A comparative analysis of low-power flip-flop designs using transmission gate-based logic." *Microelectronics Journal*, 44(3), 242-247.

https://doi.org/10.1016/j.mejo.2012.11.005

[10]. Srinivasan, S., & Chatterjee, M. (2014). "Design of a low power D flip-flop using transmission gates." *Proceedings of the IEEE International Conference on Circuits and Systems (ICCAS)*, 126-130.

#### ISSN: 2322-3537 Vol-13 Issue-02 Nov 2024

https://doi.org/10.1109/ICCAS.2014.6778 778